CoWoS 與 3D Fabric 全攻略:你需要知道的一切

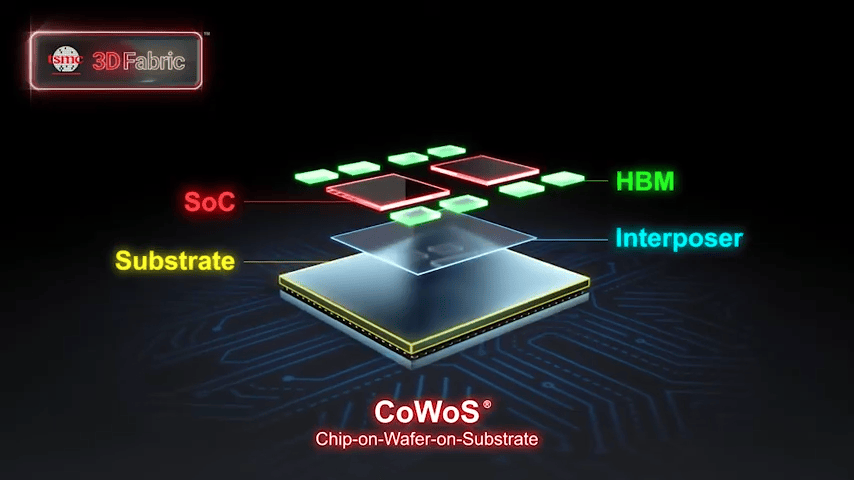

你常常聽到 CoWoS(Chip-on-Wafer-on-Substrate)和 3D Fabric 嗎?這些關鍵字最近在 AI、HPC(高效能運算)、資料中心和半導體產業超級火紅,尤其是 NVIDIA、AMD、AI 伺服器、HBM 記憶體等話題都繞不開它們。這篇用最簡單的方式,帶你一次搞懂 CoWoS、3D Fabric 技術本質、優勢、應用、產業現況,還有 Reddit 社群的真實討論氛圍。

CoWoS 是什麼?為什麼這麼重要?

CoWoS 是台積電(TSMC)發明的一種 2.5D/3D 晶片先進封裝技術,簡單說,就是把多顆晶片(像是 CPU、GPU、HBM 記憶體)透過矽中介層(Silicon Interposer)緊密地「堆在一起」再封裝到基板上。這樣做有幾個超級關鍵的優點:

超高頻寬、低延遲:晶片之間的距離變超短,數據傳輸速度快到爆,延遲也大幅降低。功耗更低:傳統多晶片系統因為連線長,耗電多。CoWoS 讓連線變短,能耗自然下降。彈性高、可擴充:可以根據需求整合不同種類、不同製程的晶片,未來要擴充也很方便。可靠度高:封裝設計進步,連接更穩定,失效率降低。

這些特性,讓 CoWoS 成為 AI 晶片、超級電腦、5G、車用電子等領域的首選封裝方案。

CoWoS 技術家族:S、R、L 各有什麼不同?

| 技術名稱 | 主要特色 | 適用場景 | 成本/產能 |

|---|---|---|---|

| CoWoS-S | 傳統矽中介層,支援多顆 HBM,頻寬最高,成本高 | AI 伺服器、HPC、NVIDIA H100/AMD MI300 | 成本高,產能有限 |

| CoWoS-R | 用有機材料(RDL)取代矽中介層,成本較低,可靠度高 | 網通、部分 AI 伺服器 | 成本較低,產能較高 |

| CoWoS-L | 加入 LSI(Local Silicon Interconnect)主動元件,彈性最大,可堆疊更多 HBM | 新一代 AI 晶片 | 預計未來主流,成本優於 S 型 |

CoWoS-S:用大面積矽中介層,支援最多 HBM 堆疊,頻寬最高,但成本和良率壓力也最大。CoWoS-R:用 RDL(再分佈層)有機中介層,成本降低、可靠度提升,適合網通或成本敏感應用。CoWoS-L:最新一代,加入 LSI 晶片橋接,能堆疊更多 HBM,設計彈性大,預期會成為未來主流。

什麼是 3D Fabric?和 CoWoS 有什麼關係?

3D Fabric 是台積電的先進封裝平台,包含三大技術:

CoWoS:多晶片堆疊在矽中介層上,主打高頻寬、低延遲。InFO(Integrated Fan-Out):無基板封裝,適合手機、輕薄裝置(像 Apple A 系列處理器)。SoIC(System on Integrated Chips):真正的 3D 堆疊,把不同晶片直接堆疊起來,密度最高。

這三種技術可以混搭,像積木一樣組合,讓設計師能針對 AI、HPC、手機、網通等不同需求,打造最適合的晶片組合。

CoWoS 的產業現狀與市場趨勢

NVIDIA 是最大用戶:2025 年全球 CoWoS 產能需求,NVIDIA 一家就佔 63%,遠超 AMD、Broadcom、Marvell 等。產能嚴重吃緊:AI 熱潮帶動需求暴增,台積電正大幅擴產,預估 2024 年底月產能達 28,000 片。應用廣泛:AI 晶片、資料中心、HPC、5G 基站、車用電子等都大量採用 CoWoS 技術。

Reddit 社群怎麼看 CoWoS 與 3D Fabric?

Reddit 上硬體社群討論 CoWoS 時,焦點多在「良率」、「可重工性」和「產業影響」:

良率與報廢問題:CoWoS 這種多晶片封裝,任何一顆晶片或連接失敗,整包就要報廢,沒辦法像傳統 SMT 那樣「重工」或「換零件」。經濟效益考量:即使理論上能重工,實際上成本太高,不如直接做新的封裝。產品分級與市場策略:有些 Reddit 用戶討論 AMD 5600X3D 這類產品,認為不是失敗品再利用,而是市場區隔與價格策略。技術發展趨勢:大家普遍認同 CoWoS 與 3D Fabric 會是未來 AI、HPC 晶片的主流,尤其是 HBM 整合和 chiplet 架構持續進化。

CoWoS 技術如何提升高效能運算應用

CoWoS(Chip-on-Wafer-on-Substrate)技術透過先進封裝設計,徹底改變高效能運算(HPC)的效能極限。這項由台積電開發的技術,核心在於將多顆晶片(如 GPU、CPU、HBM 記憶體)透過矽中介層緊密整合,創造出三大關鍵優勢:

超高速傳輸與低延遲

矽中介層搭配 TSV(矽穿孔)技術,讓晶片間連線密度達到傳統封裝的 10 倍以上,傳輸延遲降低 50%。HBM 記憶體整合:將高頻寬記憶體(HBM)直接堆疊在邏輯晶片旁,頻寬可達 1.2TB/s 以上,是 GDDR6 的 5 倍。

異質整合彈性

混合製程晶片:可將不同製程的晶片(如 5nm GPU 與 7nm I/O 晶片)整合,優化成本與效能。模組化擴充:CoWoS-L 技術透過 LSI(局部矽互連)晶片,能堆疊多達 12 個 HBM4 記憶體堆疊,滿足未來 AI 模型需求。

功耗與散熱突破

連接距離縮短 90%:傳統多晶片系統的 PCB 走線平均 10 公分,CoWoS 將距離壓縮至毫米級,功耗降低 30%。3D 堆疊散熱:TSV 結構搭配微流道冷卻技術,散熱效率提升 40%,適合 Exascale 級超算。

真實案例:NVIDIA H100 的 CoWoS 設計

整合 8 顆 HBM3 記憶體,頻寬 3.35TB/s,80 億個 TSV 連接點,中介層面積 2,700mm²,相比前代 A100,AI 訓練效能提升 6 倍。

CoWoS-S、CoWoS-R、CoWoS-L 主要差異

CoWoS-S、CoWoS-R、CoWoS-L 是台積電三種先進封裝技術,差異關鍵在於中介層材料與整合方式,直接影響效能、成本與應用場景。

CoWoS-S:矽中介層封裝(性能之王)

中介層材料:整片矽晶圓切割的中介層,搭配 TSV(矽穿孔)技術。效能表現:連線密度最高(微凸塊間距 30-60μm),頻寬達 3.35TB/s,延遲最低。適用場景:AI 伺服器、HPC(如 NVIDIA H100、AMD MI300)。限制:矽中介層脆硬,尺寸越大良率越低,成本最高(每片封裝破千美元)。

CoWoS-R:RDL 中介層封裝(成本殺手)

中介層材料:聚合物基板 + 銅導線 RDL(再分佈層),6 層銅導線結構。效能表現:傳輸速率稍低(RC 值較高),但熱膨脹緩衝優異,封裝尺寸彈性大。適用場景:5G 基站、邊緣 AI 裝置、網通設備。優勢:成本比 CoWoS-S 低 40%,可重工性較高。

CoWoS-L:混合中介層封裝(未來主流)

核心創新:局部矽互連(LSI)晶片 + RDL 層,融合 CoWoS-S 與 InFO 技術。突破性優勢:彈性擴充可堆疊 12 顆 HBM4,記憶體頻寬衝破 10TB/s;成本優化僅在高速互連區域使用矽材,整體成本比 CoWoS-S 低 25%。應用實例:NVIDIA Blackwell B200、AMD 下一代 Instinct 加速器。

| 特性 | CoWoS-S | CoWoS-R | CoWoS-L |

|---|---|---|---|

| 中介層 | 矽晶圓 | RDL 銅層 | LSI + RDL 混合 |

| 微凸塊間距 | 30-60μm | 40-80μm | 30-50μm |

| 每封裝成本 | $1,200+ | $700-$900 | $900-$1,100 |

| HBM 堆疊 | 8 顆 | 4-6 顆 | 12 顆 |

TSMC 與 ASE 的 CoWoS 聯盟 vs. 全球競爭者

台積電(TSMC)與日月光(ASE)透過 CoWoS 技術聯盟,在全球先進封裝市場建立近乎壟斷的地位。此合作結合 TSMC 的前端製程優勢與 ASE 的封測專長,形成從矽中介層到基板整合的完整供應鏈。

TSMC-ASE 聯盟的技術與產能優勢

垂直整合的 CoWoS 技術家族:TSMC 的 CoWoS 技術分為 CoWoS-S(矽中介層)、CoWoS-R(有機中介層)、CoWoS-L(混合式互連)三種架構,可依客戶需求彈性組合。ASE 則提供從 CoW(Chip-on-Wafer)前端堆疊到 oS(on-Substrate)後段封測的一站式服務。

產能壟斷與擴張速度:TSMC 2024 年 CoWoS 月產能達 28,000 片,2025 年目標翻倍至 65,000 片;ASE 2024 年投資 470 億新台幣擴充 CoWoS 產線,預計 2026 年高雄 K28 廠投產後,將吃下 TSMC 外包訂單的 40-50%。

競爭者技術與市場策略比較

三星:I-Cube 的追趕與 HBM 綁定策略:三星以 I-Cube 2.5D 封裝搭配自產 HBM3E,成功拿下 NVIDIA 部分訂單。其優勢在於垂直整合同時提供 DRAM、邏輯晶片、封裝服務,適合客製化需求。但產能僅 TSMC 的 1/4,且客戶驗證進度落後,目前市占率不足 10%。

英特爾:EMIB/Foveros 的開放生態圈:英特爾以 EMIB-T(2.5D)與 Foveros(3D)技術主攻美國市場,特點包括混合式互連 TSV 垂直導通縮短 50% 連線距離,延遲降低 15%。然而,其產能集中在美國,成本高於亞洲供應鏈,且與 TSMC 的 CoWoS 相容性有限。

安靠:區域化供應鏈的利基定位:安靠(Amkor)與 TSMC 合作在亞利桑那州建立封裝廠,專攻 InFO 與 CoWoS-R 封裝。優勢在於地緣政治紅利滿足美國客戶的「本土製造」需求,但技術層級仍落後 TSMC-ASE,且產能僅 17,000 片/月。

供應鏈與地緣戰略佈局

台灣生態系的不可取代性:從竹科到南科,TSMC 與 ASE 形成「CoWoS 產業廊帶」。矽中介層由 TSMC 獨家供應,需 65nm 製程與 TSV 鑽孔技術,良率門檻極高。ASE 在桃園、高雄、雲林佈建專廠,整合基板、測試、散熱方案。

地緣政治下的產能分流:TSMC-ASE 台灣本土占 85% 產能,另在美國/日本設廠應付「中國+1」需求。三星泰勒廠區投資 400 億美元,但 CoWoS 產線 2026 年才投產。英特爾俄勒岡州與新墨西哥州廠專注美國政府訂單,缺乏規模經濟。

未來趨勢:9 倍光罩尺寸 CoWoS

2027 年將推出的 9X 光罩 CoWoS,封裝面積達 7,722mm²,可整合 12 顆 HBM4 記憶體與 4 顆邏輯晶片,專為百億參數級 AI 模型設計。這項技術將使單一封裝的記憶體頻寬突破 10TB/s,徹底釋放量子計算與氣候模擬的潛能。

總結:為什麼你一定要懂 CoWoS 與 3D Fabric?

CoWoS 和 3D Fabric 是 AI、HPC、資料中心等高階運算核心技術,也是 NVIDIA、AMD、AI 伺服器等產業鏈關鍵。這些技術代表著未來晶片設計趨勢(chiplet、異質整合、HBM),同時是產能瓶頸與供應鏈戰略焦點。

如果你關心 AI、半導體、雲端運算、甚至是投資趨勢,CoWoS 和 3D Fabric 絕對是你必須關注的核心關鍵字!

FAQ

- 常見問題 1: COWOS 是什麼技術?回答: COWOS(Chip-on-Wafer-on-Substrate)是台積電發明的 2.5D/3D 晶片先進封裝技術,透過矽中介層將多顆晶片(如 CPU、GPU、HBM 記憶體)緊密整合,大幅提升頻寬速度、降低延遲、並顯著提升功耗效率。

- 常見問題 2: 3D Fabric 與 COWOS 有什麼關係?回答: 3D Fabric 是台積電專為先進晶片封裝設計的技術平台,包含 COWOS、InFO(無基板封裝)與 SoIC(3D 堆疊)。而 COWOS 則是其中專注於高頻寬、多晶片整合的技術,適用於 AI 伺服器及 HPC。

- 常見問題 3: COWOS 的技術類型及有何區別?回答: COWOS 可分為三種技術類型:

1. COWOS-S: 使用矽中介層,頻寬最大,適用於高效能伺服器如 NVIDIA H100。

2. COWOS-R: 用 RDL 有機層,具備更高經濟性,適合 5G、邊緣設備。

3. COWOS-L: 結合矽晶與 RDL,支援更多 HBM 堆疊,為未來主流技術。 - 常見問題 4: COWOS 如何在 AI 晶片中發揮作用?回答: COWOS 可整合 HBM 記憶體至 GPU 或 CPU 晶片旁,使頻寬超過傳統記憶體的 5 倍以上,顯著提升 AI 模型訓練及推理效能。目前 NVIDIA、AMD 等巨頭產品均採用 COWOS 技術。

- 常見問題 5: 2025 年 COWOS 市場的發展趨勢為何?回答: COWOS 市場需求持續增長,特別是來自 NVIDIA 的需求佔 63%,而台積電預計 2025 年將 COWOS 月產能擴增至 65,000 片。其應用範圍包含 AI、HPC、資料中心、5G 等高端領域。

準備迎接 AI 晶片時代的挑戰?

想要在競爭激烈的科技市場中脫穎而出?Tenten 數位行銷團隊擁有豐富的半導體產業行銷經驗,能幫助您的科技公司建立專業品牌形象、精準觸達目標客戶,並在 AI 與先進封裝技術浪潮中搶佔市場先機。無論是技術內容行銷、B2B 客戶開發,還是國際市場佈局,我們都能提供完整的數位解決方案。

立即預約諮詢,讓我們幫您打造科技業的 AI 競爭優勢!